搜寻

- 07/11/2022

【微小精确、事半功倍】Ep.2 站稳微型化的竞争能力

过去,半导体IC组件和芯片的封装大多采用标准的IC封装技术,如单芯片BGA(球栅阵列)封装。但为了响应5G、物联网、自动驾驶汽车、智能城市、远程医疗等应用的需求,这些传统的IC组件封装技术已经无法完全满足当今的高速计算和传输需求。

正因为如此,如双面成型和扇入/扇出此类的先进的系统级封装(SiP)制程,已经成为资通讯产品市场不可或缺的技术。半导体领先大厂如台积电、英特尔、三星……等,均在加速部署先进封装技术,未来如何在技术上取得突破、实现成本和性能的平衡,已成为产业最重要的发展战略之一。

有鉴于此发展趋势,自2008年起,环旭电子已开始投入系统级封装制程技术,例如高密度打件(High-Density SMT)、塑封(Molding)及屏蔽(Shielding)技术。

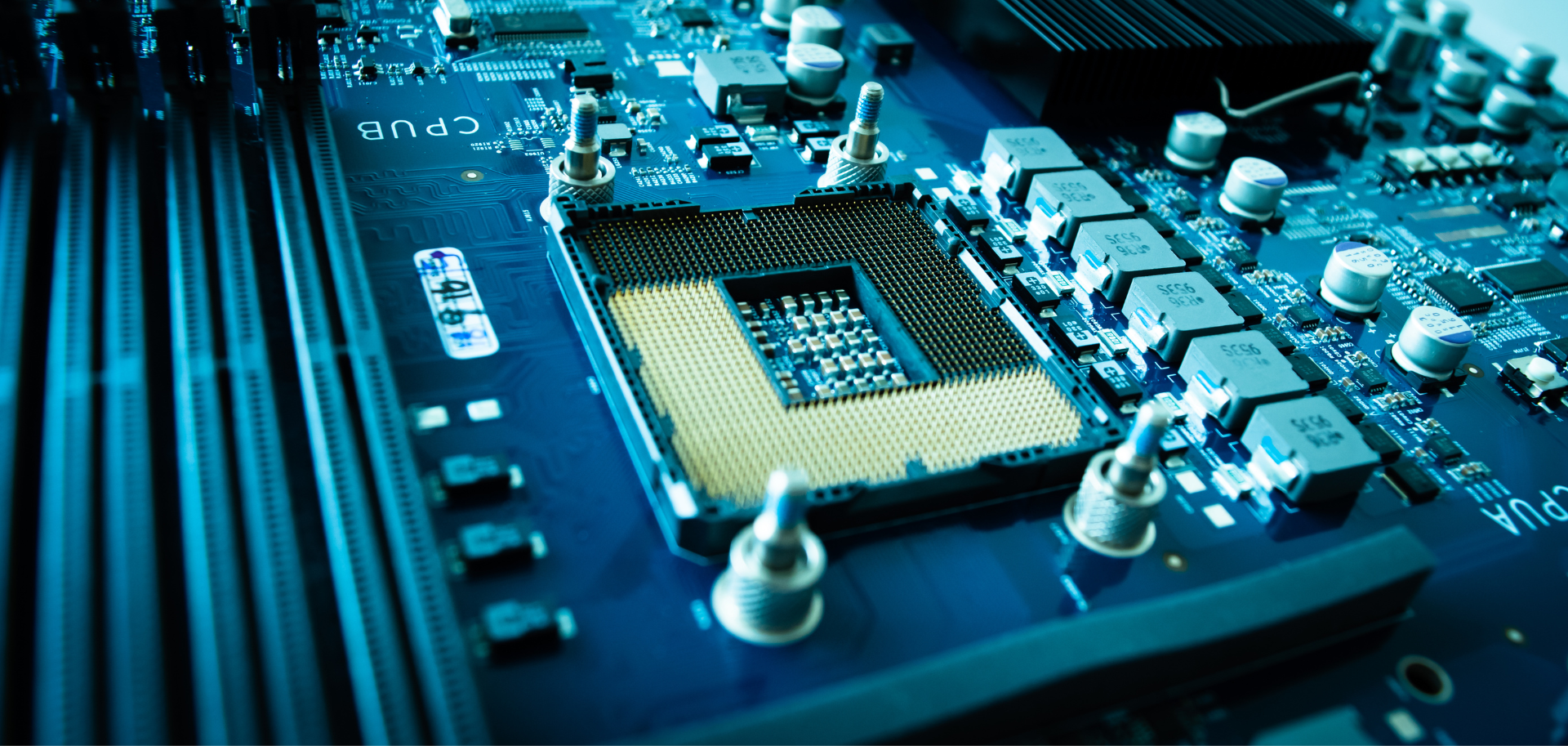

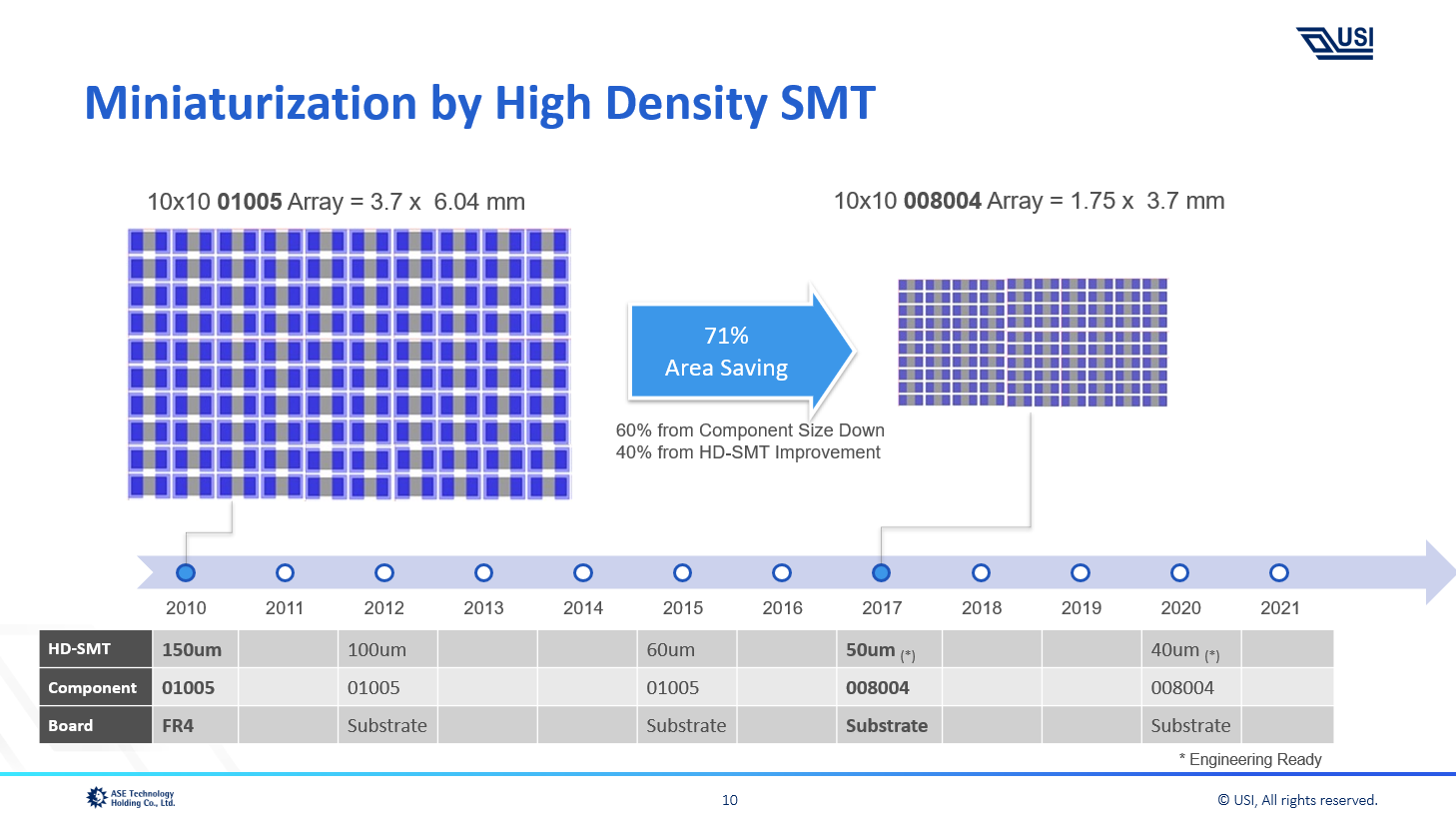

高密度打件技术

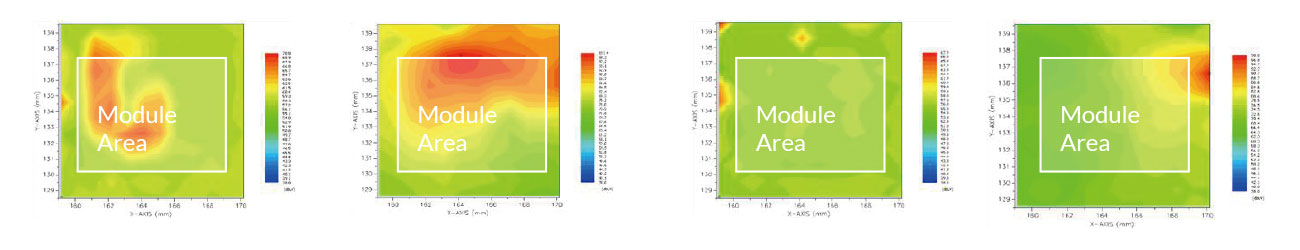

在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的最主要关键。在打件制程方面,业界普遍组件间距为150μm以上,环旭电子已达到小于成人发丝直径的50μm,显现出环旭电子在打件工艺的超高精准度。以10x10数组做比较,大幅缩减超过70%的基板尺寸,其中的40%乃源自于打件技术的突破。

深入了解更多:系统级封装 - 高密度打件能力

塑封与屏蔽技术

与传统的板阶组装相比,塑封技术是先进封装技术的一个关键分水岭,它可以有效地保护高密度封装中的微距组件,从而使得空间效率最大化。

由于高密度打件采用的是微型化元器件,因此组件与载板之间的连结,吃锡量大幅减少。为提高打件可靠度及阻抗性,避免外界湿度、高温及压力等影响,塑封制程可将完整的元器件密封包覆在载板上。以高集成的系统级封装来说,一般委外封测(OSAT)集成约100颗左右,而环旭电子目前的技术可容纳高达900颗组件。

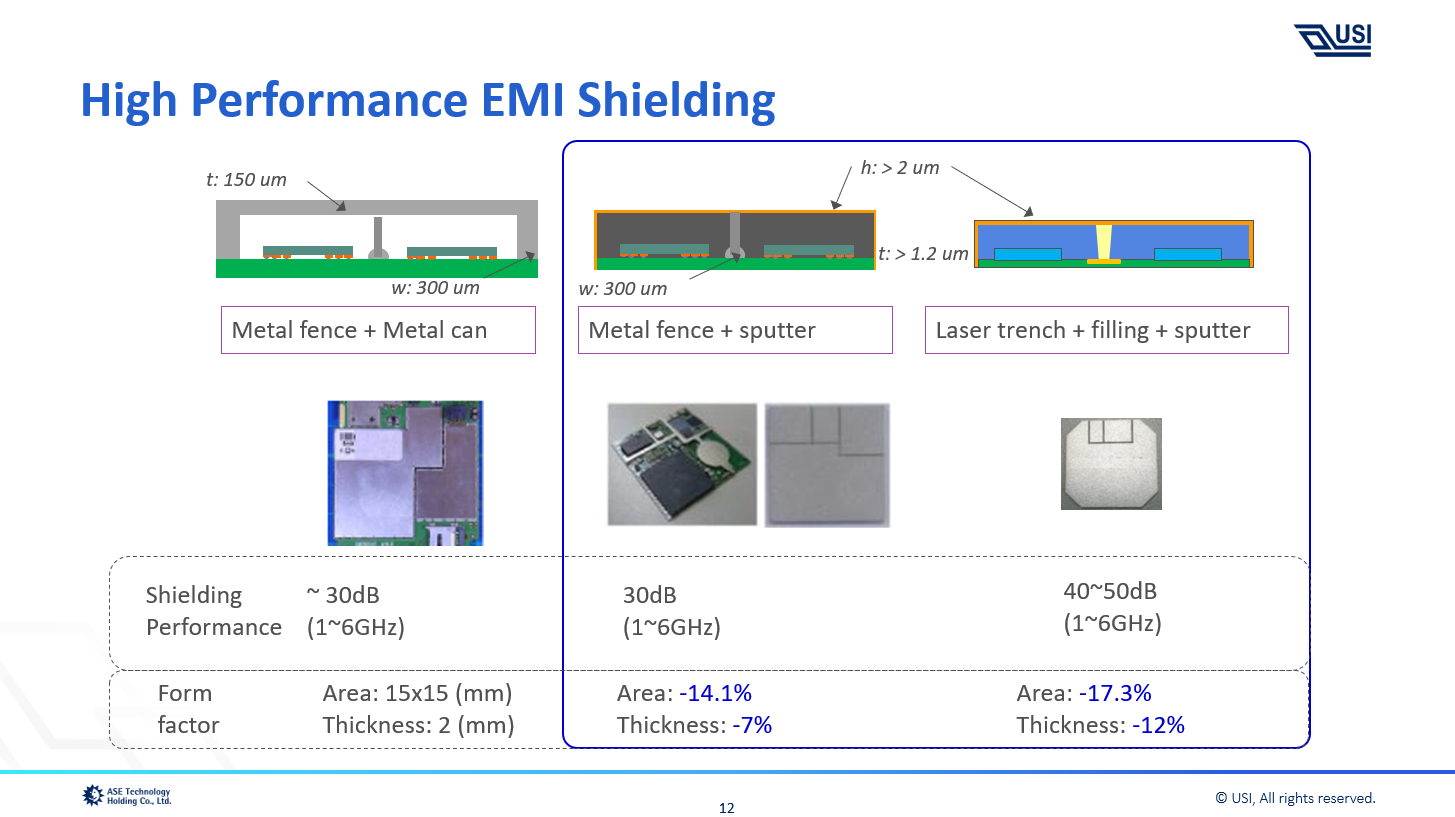

另一方面,要将上百颗电子组件塑封,则需要屏蔽来隔离电子组件间的讯号,避免互相干扰。环旭电子所开发的共形、分段型屏蔽皆可达到小于2μm,为其他组件腾出超过17%的空间,并可屏蔽40-50 dB的电磁干扰。

对于寸土寸金的微型化模块来说,减少150μm的厚度是一大进步。此外,塑封和组件之间的顶部和侧面空间也可以再减少,进一步降低厚度与缩小面积。

深入了解更多:系统级封装 - 塑封能力、系统级封装 - 屏蔽能力

站稳微型化世界的竞争力

随着时代演进,科技产品更加强调轻便型与功能性的结合,因此产品所能使用的空间更是寸土寸金,透过系统级封装制程,整体可节省约30-40%的板面积,凭借着微型化及模块化的异质整合优势,板端、天线及机构的设计整合上更加有弹性,这是IC制程所做不到的。

先进封装技术的突破正在影响产业供应链、改变竞争格局,面对微型化时代的来临,微型化技术已然成为不可或缺的竞争力。环旭电子从WiFi产品就开始进行布局、站稳脚步,凭借多年积累在射频、穿戴式装置等产品的丰富制程经验,以及持续突破的技术,准备迎接这一场全球关注的「毫厘之争」。

跟紧产业脉动

随时掌握第一手产业创新科技、应用与深度新闻

订阅 USI 博客

随时掌握第一手产业创新科技、应用与深度新闻